Характеристики

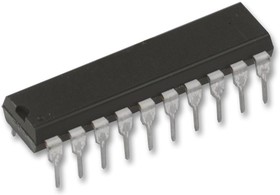

SN74HCT240N, АП3The SN74HCT240N is an octal Buffer/Line Driver designed specifically to improve both the performance and density of 3-state memory address drivers, clock drivers and bus-oriented receivers and transmitters. The HCT240 device is organized as two 4-bit buffers/drivers with separate output-enable (OE) inputs. When (OE) is low, the device passes inverted data from the A inputs to the Y outputs. When (OE) is high, the outputs are in the high-impedance state.

• Inputs are TTL-voltage compatible

• 3-State outputs drive bus lines or buffer memory address registers

• High-current outputs drive up to 15 LSTTL loads

• 80µA maximum ICC low power consumption

• 12ns typical Propagation delay (tpd)

• ±6mA Output drive at 5V

• 1µA maximum Low input current

Микросхемы / Логические микросхемы / Микросхемы ТТЛ (серия 74)

Корпус: 20-PDIP, инфо: Логический элемент ТТЛ инвертер двойной с 4 входами КМОП кристалл, примечание: АП3

Личный кабинет

Личный кабинет

Загрузка

Загрузка